![]()

Pour réaliser un compteur asynchrone, il suffit de cascader des diviseur par deux qui réagissent sur front descendant :

Le schéma pour un compteur trois bits est :

La simulation donne les résultats suivants :

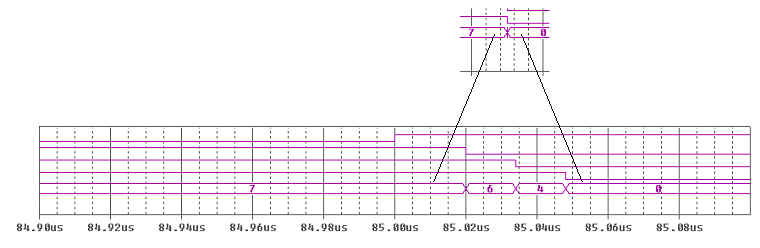

Entre l'état 1 et l'état 2 ou entre l'état 3 et l'état 4 ainsi qu'entre l'état 5 et l'état 6, il apparaît des états parasites. En effet si un zoom entre l'état 7 et l'état 0 est effectué :

Il faut apparaître des états parasites de comptage 6 et 4 qui ne devrait pas exister en théorie. Ce problème fait que les compteur asynchrone ne sont pas utiliser en compteur mais en diviseur de fréquence. Lorsqu'il sera nécessaire d'utiliser une compteur, les compteur synchrones seront choisis.

Les compteurs asynchrones/diviseurs de fréquence existe sous forme intégré. C'est le cas du circuit 74LS90. Il s'agit d'un compteur modulo 10 sur 4 bits : QA, QB, QC, QD où QD est le point fort. Il possède deux horloges : l'horloge de la première bascule CKA et l'horloge de la seconde bascule CKB. Si QA est relié à CKB, le compteur fonctionne en compteur modulo 10. Sinon, le compteur est constitué d'un diviseur par deux et d'un diviseur par cinq.